ロジックアナライザーの製作

ロジックアナライザーの製作

はじめに はじめに・・・・・・・ というわけで路地穴(logic analyzer)をつくります。 (どういう訳?単なる物欲だったりして?) イヤ、別に訳などなく、ただ作りたかったので作りました。回路は約10年前に仕事で、製作した試験装置を参考にすればよいことはわかっているのであとは根気だけ・・・しかし、年寄りのこと老眼が進んでハンダ付けが悩ましい。何かハードウェアを簡単に作成する方法はないものかと考えて、ザイリンクスのCPLDを使うことにしました。カメレオンUSBという手もありますが、ない頭を絞って作るというのがモットーなので・・・・ 参考にしたページは Sazanami Online 森の電脳総合病院 金野研のホームページ などです。 |

|

|

ロジックアナライザー 等価回路

|

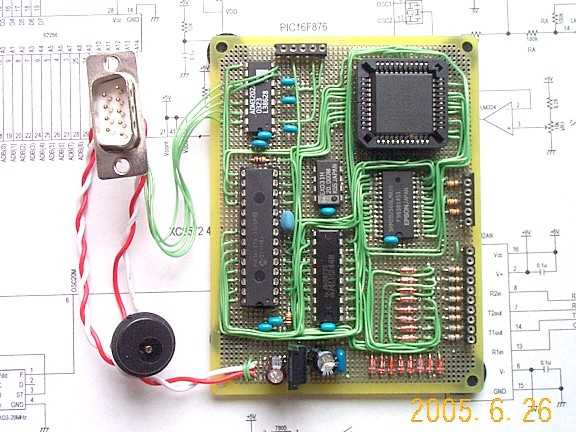

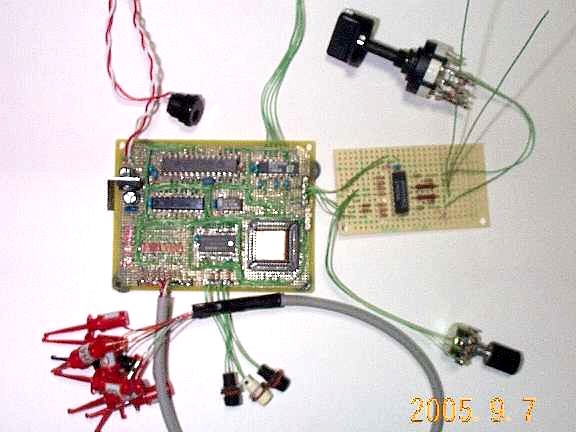

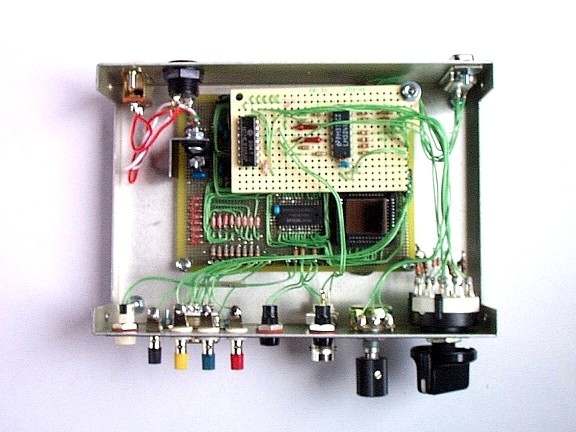

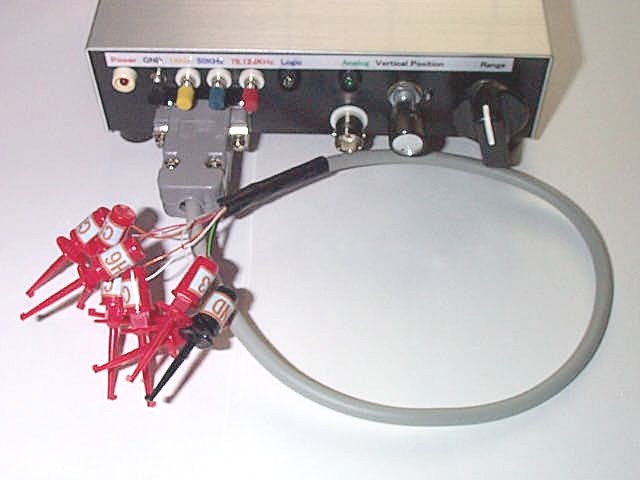

仕様 仕様はじめに、BLUE BACKSのCDROM付電子回路シミュレータ入門のCircuitMaker6.0を用いて、シミュレーションをしました。左にその回路図がありますが、クリックして別ページで見てください。また、後のドキュメントにシミュレーションファイルを提示してありますので、ダウンロードしてCircuitMaker6.0でシミュレーションしてみてください。回路の説明はハッキリ言ってメンドウ・・・・・ レベルでトリガーする場合、Hレベル(あるいはLレベル)の間だけしかサンプリングしない回路になっているモノがありますが、トリガー後レベルが反転すると波形の記録が出来なくなってしまう。なので、レベルでトリガーする場合もラッチしています。それからトリガーとサンプリングの開始が同期していないため、サンプリング周波数が低くなると、トリガー時点の波形を取りこぼす可能性が大きくなります。このような不具合をなくすため、サンプリング周波数に関係なく、トリガー後最大0.15μsec以内に最初のサンプリングを行うようにしてあります。このあたりの考え方は、約10年前に製作した試験装置と同じです。また、RAMのWE信号をLowに固定したまま、アドレスのカウントだけで書き込みを行っているモノもありますが、RAMのデータシートにはそのような使用法は書かれていません。たとえシロートザイクとは言え、メーカーが保証する範囲で使用するのが正しい方法と思います。ここではRAMに対するWE信号はサンプリング周波数に関係なく、常に75ns(理論値)、使用したRAMのアクセスタイムは55nsです。小さく安く作ることに徹するため、RAMのアドレスはPICに接続しません。言い訳を言えば、ロジアナでは32Kワードをすべて使用しても、測定にかかる時間は人間レベルからいえば瞬時ですから、パソコンから読み出す場合のみPIC内でアドレスを管理できれば良く、RAMのアドレス信号を直接読む必要はありません。RAMのアドレス信号という足枷がなくなったので(?)PICは28PINのPIC16F876、CPLDはXC9572-44Pということで回路設計を行いました。できあがった回路図を見ると、PICに3本の余裕が・・・ということでオシロスコープ機能を追加。以前に製作したオシロスコープの1CH分の回路をコピーして、CPLDに多少機能を追加して完成。外部にRAMを設けているため、サンプリング周波数も最大20KHzと、以前に製作したオシロスコープより約20倍性能がアップ。1CHとは言え、これで以前に製作したオシロスコープは出番がなくなりそう。 測定はパソコン上で条件を設定後、Settingボタンをクリックして条件を本体に送信します。その後、Runボタンのクリックで測定を開始します。アナログ時は測定中止が可能です。中止した時点までのデータが読み出されて、画面に波形が描かれます。ロジアナ時は基本的に測定中止はできません、測定時間が前述したように短いので人間技ではムリですから。ただし、トリガーを待っている時は中止できます。この場合は当然ですが、測定が開始されていないためデータの読出しはしません。カーソルの移動は右ボタンのドラックで基準線(黒)、左ボタンのドラックで測定線(赤)が移動します。マウスカーソルがロジック部にあるときは時間軸が、アナログ部にある場合はアナログ電圧軸のカーソルが移動します。アナログの入力レンジはアナログ時に自動的に読込を実行しています。この機能のため、回路上苦肉の策というか・・手持ちの74LS125を使いましたが、オープンコレクタ出力のORゲートがあればダイオードは必要ないのですが、マァ、たいしたことではないのでヨシとしましょう。 基準波形出力(つまりキャリブレータのことです) 78.125KHz,50KHz,1KHz 電圧は・・・CPLDと水晶発信器の出力そのままなのでイイカゲン? ロジアナ部 サンプリングデータ:8CH 32Kワード サンプリング周波数:10MHz,5MHz,2MHz,1MHz,500KHz,200KHz,100KHz,50KHz トリガー:H/Lレベル,H/L立ち上がり 1CH〜4CHのどれか :1CH〜4CHの4Bitのパターン 等しい時,等しくない時,等しくなった時,等しくなくなった時 (解り難い表現ダナァ?!) アナログ部 分解能:8Bit A/Dコンバーター 16Kワード サンプリング周波数:20KHz,10KHz,5KHz,2KHz,1KHz,500Hz,200Hz,100Hz トリガー:ありません。測定開始でフリーランニング (残念ですが仕様です、ホンネはできなかったから?) 改良版はH/Lレベル,H/L立ち上がり)とフリーラン 10/30改良 入力電圧:±0.5V,±2.5V,±5V,±10V,±25V ±EVは0Vから2×EVまででもイイですよ、わかりますヨネ。 ex.±25Vは0Vから50Vまで  製作 製作毎度のことながら、あまりきれいな作りではありません、参考程度に。今回はラベルらしきものを貼って見ました。ホンネを言えば自分が忘れた場合のためにだったりして?!マルキン’ず工房のバナーを貼ってみましたが、娘にカッコワルーーーって 徒し事はさておき、重要な部品の詳細を書いておきましょう。と言っても重要なのはアクセスタイム55nsのRAMだけです。秋月から購入した3ケ400円のEPSON製SRAM SRM2B256SLMX55。 アナログ部のOPアンプ廻りの抵抗は精度の良いものを使ってください。以前に製作したオシロスコープのページにも書きましたが、精度の良い抵抗を使えば無調整でも精度良く電圧を測定できるように抵抗値を計算しています。もちろん、E系列の抵抗値になっていますから、ご安心を!(670Ωなどというこの世に存在しない抵抗は使っていませんから)前述したように、アナログ部は後から思いついて(思いつき?だったりして)追加した機能なので、別基板になっています。カッコ悪いし、ノイズ上もよくないので作りたい人は1枚の基板で作りましょう。プローブはジャンク屋サンで買った10芯のシールドケーブルで作りました。20MHzの水晶発信器はKSS社製のEXO-3。発光ダイオードは高輝度型、本来はなくても良いので電流は少なめにしましょう。CPLDは発熱します。ホームセンターなどで売っているアルミのアングル材を適当な長さに切って、CPLDに貼り付けました。3端子レギュレータにも同様に取り付けています。  ドキュメント ドキュメント関連するドキュメントはすべて公開します。 (オォォォーーー!!大盤振る舞いだーーァ?) CircuitMaker6.0 シミュレーションファイル ファイルをダウンロードして、CircuitMaker6.0でシミュレーションすればCPLD内部の動作が理解できると思います。 ロジックアナライザー 回路図 言わずと知れた、回路図です(?) ロジックアナライザー パターン 毎度のことながら、パターンと言えるほどのものではありません。大体の部品配置程度です。 ロジックアナライザー 筺体 これもまた、イイカゲンな図面です。参考程度に!? CPLDプロジェクトファイル一式 プロジェクトに必要なファイル一式を圧縮してあります。シミュレーション用も入っています・・・テキトウデスガ?! PIC16F876 ソースリスト 10/27 修正 PIC16F876 HEXファイル 10/27 修正 上記2つのファイルはPIC16F876用、PICに書き込むのはHEXファイルですヨ! (ASMファイルを焼こうとした人がいるとかいないとか?) 10/27 立ち上がりのトリガー動作に不具合があったので修正しました。 ロジックアナライザー VB実行ファイル ロジックアナライザー VBソースリスト 上記2つのファイルはパソコン用、VB6SP6環境で動作します。ソースリストは圧縮してあります。 キャリブレータ(1KHz)のオシロスコープ測定結果 測定した結果をHDDに保存したファイルです。キャリブレータ(1KHz 周期1msec)をオシロスコープで測定しました。上記VB実行ファイルでLOADすると波形が描かれて、1msecで正しく測定できていることが確認できます。 |

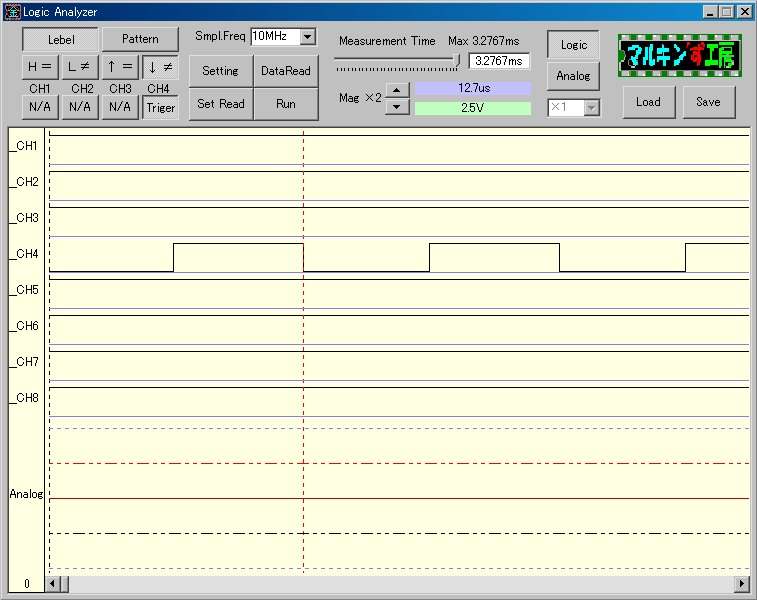

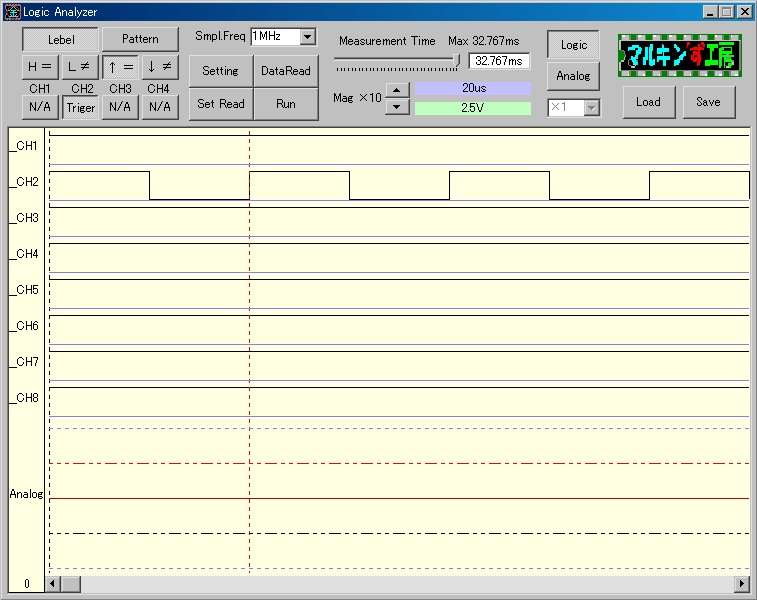

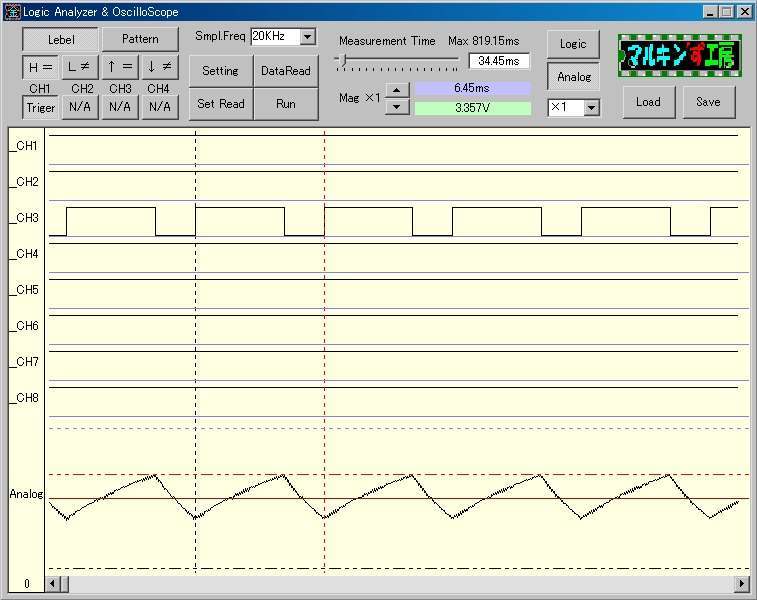

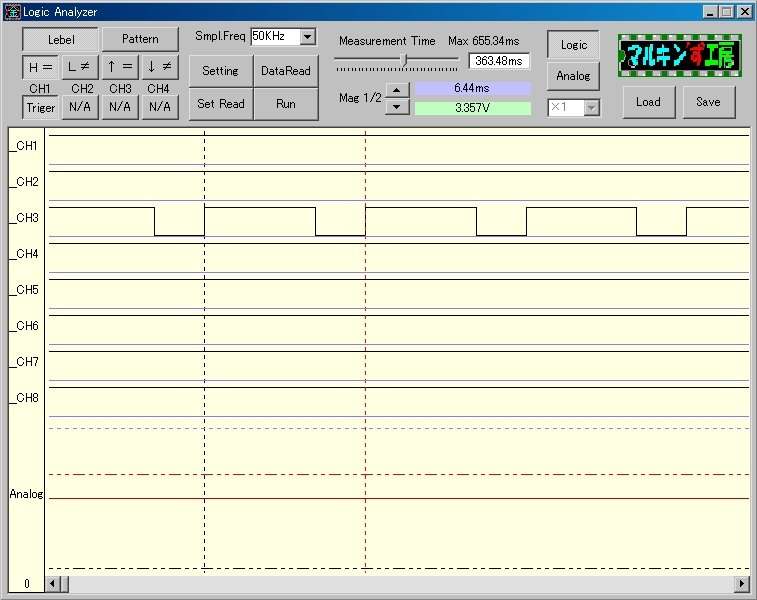

測定結果 測定結果測定結果-1 78.125KHz 12.8μsec 立下りエッジでトリガーをかけて測定。12.8μsecに対してトリガー時点の誤差はこの結果では0.1μsec。トリガー後は正しく12.8μsecです。 測定結果-2 50KHz 20μsec 本ロジアナではトリガー時点の誤差はサンプリング周波数に関係なく一定(最大0.15μsec)ですから、サンプリング周波数が低くなるとトリガー時点の誤差は埋没(?)してしまい、測定結果に出てきません。この測定では、トリガー時点でも20μsecと誤差なしで測定されています。 測定結果-3 555発信回路出力 オシロスコープで測定 測定結果-4 555発信回路出力 ロジアナで測定 555(わかりますヨネ、わからない人は毎度のこと、自分で調べて!)でテキトーな発信回路を作って、アナログ測定してみました。コンデンサには電源電圧の1/3から2/3まで充電され、2/3から1/3まで放電を繰り返していることが確認できます。このときの周期は6.45msec。アナログ時のサンプリング周波数20KHzはPIC16F876にとっては最も忙しい(?)条件です。これをロジアナで測定した結果が次の波形で、周期6.44msecですから最も忙しい(?)条件のアナログ測定でも、それなりに正しく測定できていると考えて良いでしょう。メデタシ!メデタシ! |

|

|

測定結果-1 78.125KHz 12.8μsec 測定結果へ戻る

測定結果-2 50KHz 20μsec 測定結果へ戻る

測定結果-3 555発信回路出力 オシロスコープで測定 測定結果へ戻る

測定結果-4 555発信回路出力 ロジアナで測定 測定結果へ戻る |

|

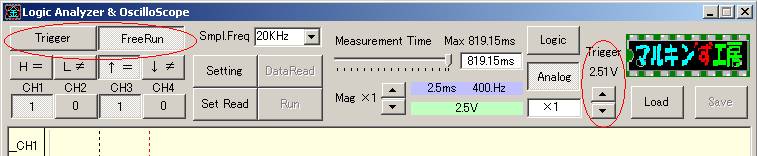

アナログ部の改良 アナログ部の改良アナログ部にトリガー(H/Lレベル、H/L立ち上がり)とフリーランの機能を追加しました。トリガー電圧はAnalog選択ボタンの右側にあるUpDownコントロールで設定します。また、パソコンとの通信速度を115200BPSにし、データの読み込み時間を短縮しました。 改良前のSaveしたデータはデータ量が異なるため、改良版では正しくLoadできません。再度測定し、Saveし直してください。 下記リンクからファイルをダウンロードし、PIC16F876を焼き直してください。当然ですが、改良前と改良版の組み合わせでは正しく動作しませんので、VB実行ファイルもダウンロードしてください。 |

|

| 改良版 PIC16F876 HEXファイル 改良版 ロジックアナライザー VB実行ファイル

アナログ部の改良 |

|

20MHzに改造 20MHzに改造秋月から購入した3ケ400円のEPSON製SRAM SRM2B256SLMX55は、アクセスタイムが55nsのため最高サンプリング周波数は10MHzにしましたが、自作のガラクタCNC基板製作機を製作する過程でスキャナーのガラクタを購入し分解したところ、アクセスタイムが35nsの同種のSRAMを見つけました。そこで早速、20MHzに改造してみました。CPLDとパソコン側のプログラムを修正し、アッという間に完成。ただし、アナログ部のサンプリングはPICのソフトのみで行っているため、アナログ部のサンプリング周波数は変更ありません。ところで、秋月のWebカタログを見ていたらKSS社製のEXO-3 20MHzの水晶発信器が新商品として販売されていました。ウーーン、もっと早く販売されていたら、腐りかけのモノを使わずに済んだのに・・・・・・ オジサンはこの水晶発信器がスキ!?CANタイプの水晶発信器はどうもなじめない? そういうわけで20MHzに改造後のサンプリング周波数は20MHz,10MHz,5MHz,2MHz,1MHz,500KHz,200KHz,100KHzになります。 下記リンクからファイルをダウンロードし、CPLDを焼き直してください。当然ですが、10MHz版と20MHz版の組み合わせでは正しく動作しませんので、VB実行ファイルもダウンロードしてください。PICのプログラムは変更ありません。回路も変更なしです。 半田鏝を持たずに、ハードウエアの機能を変更出来るCPLDはスゴイ!!! 20MHz版 CPLDプロジェクトファイル一式 20MHz版 ロジックアナライザー VB実行ファイル 改良版 PIC16F876 HEXファイル 10MHz版と変更はありません |

|

纏め 纏め10年以上前に設計などという仕事をしていた時、研報なるものを書くと“隘路になったこと”という項目があったことを思い出したので、今回の製作時に隘路になったことを。ロジアナ部が出来たので早速動かしてみたが、まったく動作せず????(イヤラシイ言い方をすれば)オジサンは基板の製作でほとんど間違えたことがないので、アレッ?何か狐にバカにされたみたいな・・・配線は作りながら導通チェッカーで確認しているし、CPLDはCircuitMaker6.0とWebPackでシミュレーションしてうまくいっている。PICのプログラムは複雑なことをしているわけではないので、ソースリストを確認する限りおかしなところはないようだ。回路の間違い?回路図を睨んでいたら、オープンドレインという言葉が頭の片隅を過ぎった。オッ、憎っくきRA4、オマエはオープンドレインだったはず。データシートを見ると確かにオープンドレイン。というわけで10KΩで5Vに接続、その他はどうということもなく素直に意図した通りに動きました。隘路ではなく手間取ったのはアナログ時のサンプリング周波数を合わせるため、タイマー割込みの時間を微調整したところ。20KHzのタイマー割り込みは計算上50μsecだが、Timer0に設定値を書き込むと2サイクル分カウントしない、割り込みを受け付けてから設定値を書き込むまでに何サイクルかは進んでいる、こういった処理遅れを考慮すれば50μsecより短くする必要があリます。今回は47μsecで20KHzが得られました。 娘にバカにされたけど、それなりに満足!!!なものが出来たかナ? |

|